For the long Easter weekend I have organized a new toy: the NXP LPC55S69-EVK board: a dual ARM Cortex-M33 running at 100 MHz with ARM TrustZone:

The LPC55S69 is of special interest because it is one of the new ARM Cortex-M33 which implements new ARM Trustzone security features: with this feature it is possible to run ‘trusted’ and ‘untrusted’ code on the same microcontroller.

The following table from ARM (https://developer.arm.com/ip-products/processors/cortex-m/cortex-m33) gives an overview of the Cortex-M33 (Armv8-M) architeture:

| Feature | Cortex-M0 | Cortex-M0+ | Cortex-M1 | Cortex-M23 | Cortex-M3 | Cortex-M4 | Cortex-M33 | Cortex-M35P | Cortex-M7 |

| Instruction set architecture | Armv6-M | Armv6-M | Armv6-M | Armv8-M Baseline | Armv7-M | Armv7-M | Armv8-M Mainline | Armv8-M Mainline | Armv7-M |

| Thumb, Thumb-2 | Thumb, Thumb-2 | Thumb, Thumb-2 | Thumb, Thumb-2 | Thumb, Thumb-2 | Thumb, Thumb-2 | Thumb, Thumb-2 |

Thumb, Thumb-2 |

Thumb, Thumb-2 |

|

| DMIPS/MHz range* | 0.87-1.27 | 0.95-1.36 | 0.8 | 0.99 | 1.25-1.89 | 1.25-1.95 | 1.5 | 1.5 | 2.14-3.23 |

| CoreMark®/MHz** | 2.33 | 2.46 | 1.85 | 2.5 | 3.34 | 3.42 | 4.02 | 4.02 | 5.01 |

| Pipeline stages | 3 | 2 | 3 | 2 | 3 | 3 | 3 | 3 | 6 |

| Memory Protection Unit (MPU) | No | Yes (option) | No | Yes (option) (2 x) |

Yes (option) | Yes (option) | Yes (option) (2 x) |

Yes (option) (2 x) |

Yes (option) |

| Maximum MPU regions | 0 | 8 | 0 | 16 | 8 | 8 | 16 | 16 | 16 |

| Trace (ETM or MTB) | No | MTB (option) | No | MTB (option) or ETMv3 (option) |

ETMv3 (option) | ETMv3 (option) | MTB (option) and/or ETMv4 (option) |

MTB (option) and/or ETMv4 (option) |

ETMv4 (option) |

| DSP | No | No | No | No | No | Yes | Yes (option) | Yes (option) | Yes |

| Floating point hardware | No | No | No | No | No | Yes (option SP) | Yes (option SP) | Yes (option SP) | Yes (option SP + DP) |

| Systick Timer | Yes (option) | Yes (option) | Yes (option) | Yes (2 x) | Yes | Yes | Yes (2 x) | Yes (2 x) | Yes |

| Built-in Caches | No | No | No | No | No | No | No | Yes (option 2- 16kB | Yes (option 4-64kB |

| I-cache | I-cache, D -cache) | ||||||||

| Tightly Coupled Memory | No | No | Yes | No | No | No | No | No | Yes (option 0-16MB I-TCM/D-TCM) |

| TrustZone for Armv8-M | No | No | No | Yes (option) | No | No | Yes (option) | Yes (option) | No |

| Co-processor interface | No | No | No | No | No | No | Yes (option) | Yes (option) | No |

| Bus protocol | AHB Lite | AHB Lite, Fast I/O | AHB Lite | AHB5, Fast I/O | AHB Lite, APB | AHB Lite, APB | AHB5 | AHB5 | AXI4, AHB Lite, APB, TCM |

| Wake-up interrupt controller support | Yes | Yes | No | Yes | Yes | Yes | Yes | Yes | Yes |

| Integrated interrupt controller | Yes | Yes | Yes | Yes | Yes | Yes | Yes | Yes | Yes |

| Maximum # external interrupts |

32 | 32 | 32 | 240 | 240 | 240 | 480 | 480 | 240 |

| Hardware divide | No | No | No | Yes | Yes | Yes | Yes | Yes | Yes |

| Single cycle multiply | Yes (option) | Yes (option) | No | Yes | Yes | Yes | Yes | Yes | Yes |

| CMSIS Support | Yes | Yes | Yes | Yes | Yes | Yes | Yes | Yes | Yes |

(ARM Cortex-M Comparison Table: Source ARM).

Unboxing

I ordered my board from Mouser for CHF 43. The board came in nice card box:

The content (apart of some stuffing material) is the board itself plus a small bag with 4 jumpers:

The board includes a LPC4322 (Link2) based debug probe:

Software and Tools

On https://mcuxpresso.nxp.com there is the MCUXpresso SDK for the board available for download:

I have downloaded the latest version 2.5.1 (released mid of April 2019):

As IDE I’m using the NXP MCUXpresso IDE 10.3.1. The SDK gets installed by Drag&Drop into the Installed SDK’s view:

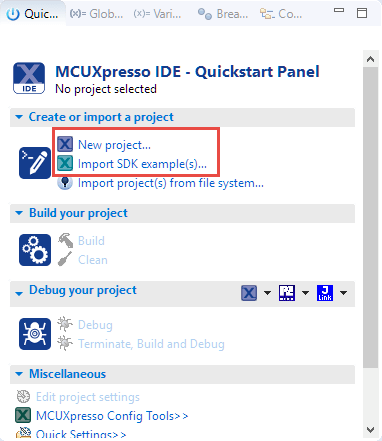

With the SDK installed, I can quickly create a new project or import example projects:

FreeRTOS

The SDK V2.5.1 comes with a FreeRTOS V10.0.1 port which runs out of the box, using the M4 port.

In the McuOnEclipse FreeRTOS port I’m already using FreeRTOS 10.2.0, so this is something I have to soon too.

Configuration Tools

The IDE comes with the NXP MCUXpresso Configuration Tools integrated.

With the graphical configuration tools I can create pin muxing and clock configurations:

Secure and Non-Secure

The SDK comes with demos using secure + non-secure application parts. To make it easy, the projects have TrustZone settings for the compiler and linker:

I have started playing with TrustZone, but this is subject of a follow-up article.

Erase Flash

Dealing with a ARM Cortex-M33 multicore device for sure is a bit more complex than just using an old-fashioned single Core M0+. Because of the secure and non-secure features, it might be necessary to get things back into a clean state. So this is what worked best for me:

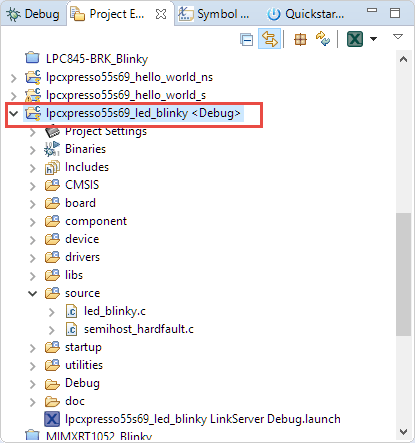

- Have a non-secure and simple project present in the workspace. I’m using the ‘led_blinky’ from the SDK examples.

- Power the Board with IP5 USB connector (P5: cable with the yellow dot) and debug it with the onboard LPC-Link2 connector (P6).

- With that project selected, erase the flash using the action in the Quickstart Panel.

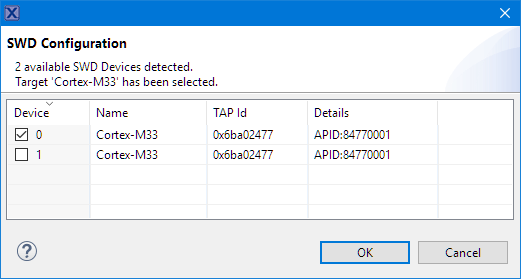

- Select core 0 for the erase operation:

- This should work without problems.PressOK the dialog:

- At this point I recommend to disconnect and re-connect the P6 (Debug) cable.

- Now I can program the normal application again:

With this I have a working and known state for my experiments.

Summary

The Easter break is coming to an end and has been interesting at least to say. The NXP LPC55S69-EVK is very appealing: the board is reasonably priced and with all the connectors it is a good way to evaluate the microcontroller. The most interesting thing is that it has a dual-core ARM-Cortex M33 with the ARM TrustZone implementation. To be able to run ‘trusted’ and ‘untrusted’ (e.g. user code) on the same device could be one of the standard models of microcontroller going forward, especially in the ‘internet of things’ area. So I think I have to explore this device and board and its capabilities in at least one follow-up article?

Happy Trusting 🙂

Links

- NXP LPC55S69-EVK web site: https://www.nxp.com/part/LPC55S69-EVK

- ARM Trustzone for Cortex-M: https://www.arm.com/why-arm/technologies/trustzone-for-cortex-m

- MCUXpresso SDK: https://mcuxpresso.nxp.com

- GDB All-Stop and Non-Stop Mode with LinkServer

- Better FreeRTOS Debugging in Eclipse

I just had a NXP training on this board last week in Minneapolis. Wow, what a part.

It has some very interesting hardware on it like a very interesting DSP implementation that isn’t mainstream at all. The memory protection stuff is something closer to what’s been around in minicomputers for 45 years but hasn’t been coming to the microcontroller land. This has lots of crypto stuff on it. It has odd things like IIR engines. The SDK now knows how to slice things up for the hardware.

Yah, if you’re doing DSP kinds of things on the edge in IoT land, this processor is exactly what is required.

LikeLike

The ARM default memory protection say for the M4 has been kind of useless to me. The NXP extensions on it (I used it on the K64F) made it at least somewhat usable with a better/finer memory granularity. I think that might be one of the reasons that the standard ARM Cortex MPU (or even the extensions) have not been used much in the industry. I have not yet looked what the LPC55S69 offers in that space.

About the DSP implementation: I have not used something like this in my projects, but I guess with all the ‘Alexa & Co.’ stuff getting in more places, maybe this would be the target market for this?

As for trainings on the LPC55S69: I looked what is available in Europe, and obviously Avnet is running a a series (https://www.avnet.com/wps/portal/silica/resources/training-and-events/event/nxp-lpc55xx-hands-on-training/) with Milan the closest. Unfortunately I’m tight up on that date at the university so I’m exploring things on my own. Who did the training in Minneapolis? Is there material availble somewhere? I had sucess playing with one of the secure/unsecure examples with some clues from the forums.

LikeLike

Thanks Erich! Are you going to explore multi-processor FreeRTOS applications, in addition to trust management?

Thanks again,

Best Regards, Dave

LikeLike

Hi Dave,

you mean running FreeRTOS kernel on one core and tasks on another? I did not had that in mind.

LikeLike

Pingback: Internal and External Debug Options for the NXP LPC55S69-EVK Board | MCU on Eclipse

Pingback: TrustZone with ARMv8-M and the NXP LPC55S69-EVK | MCU on Eclipse

Pingback: Introducing Mark’s Video Guest Blog | MCU on Eclipse

Pingback: Open Source LittlevGL GUI Library on Adafruit Touch LCDs with NXP LPC55S69-EVK | MCU on Eclipse

Pingback: MCUXpresso IDE V11.1.0 | MCU on Eclipse

Pingback: New MCU-Link Debug Probe from NXP | MCU on Eclipse