The first FRDM-KL25Z Freedom Logic Analyzer firmware was missing one important feature: Triggers! But this weekend the firmware has evolved a bit :-).

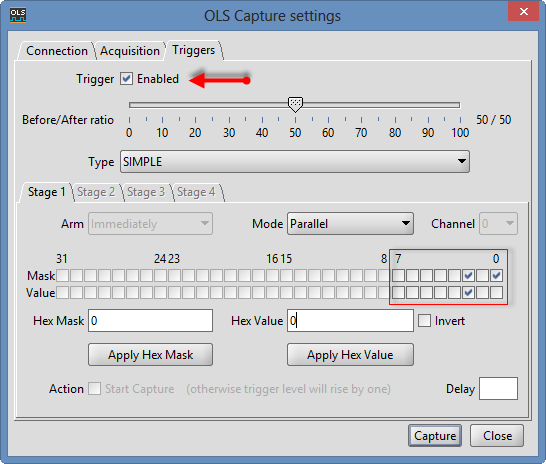

Triggers

Currently up to 8bits are supported, and only ‘Stage1’ triggers in Parallel mode. So no sequencing yet. With enabled triggers, data capturing is waiting until the value bits are matching the mask bits: (data&maskBits)==valueBits. The ‘before’ and ‘after’ ratio is not supported yet.

Sampling Rate

It is possible to select a sampling rate. Right now 100 kHz and 200 kHz are implemented:

💡 I was able to get up to 200 kHz sampling rate with the trigger code added. It should be possible to get higher rates with optimizations enabled or reducing the interrupt load.

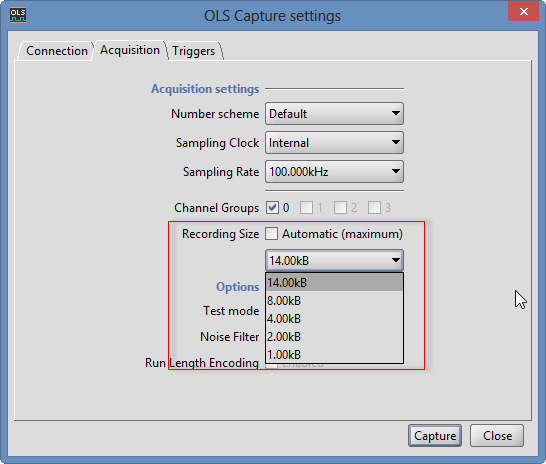

Recording Size

The client now offers as well different recording sizes. Although the buffer on the Freedom board always have the same size (that option reduces the amount of data transmitted to the OLS client):

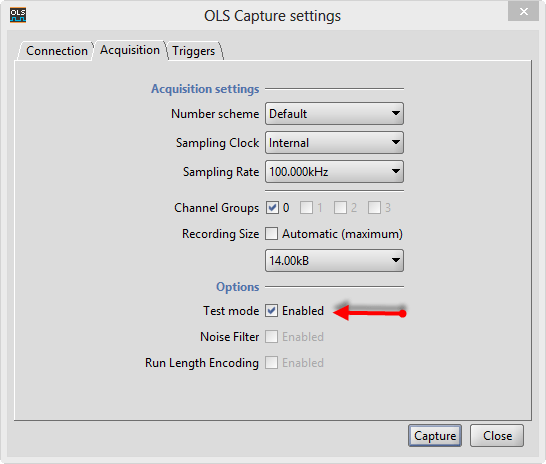

Test Mode

And finally: The test mode functionality is implemented now:

With test mode enabled, the device returns test data instead of real data from the probes:

Firmware

The firmware (CodeWarrior project) and updated configuration file is available here on GitHub.

Happy Triggering 🙂

PS: Many thanks to Rainer Geiger who provided me his implementation of triggers of the SUMP protocol!

Pingback: Tutorial: PWM with Processor Expert | MCU on Eclipse

Pingback: Freedom Logic Analyzer with DMA | MCU on Eclipse

Pingback: Freedom Logic Analyzer with DMA | minghuasweblog