Open Source software has been around for decades. But open source on hardware especially microcontroller is not much a reality these days. But there is something which might change this: RISC-V is a free and open RISC instruction set architecture and for me it has the potential to replace some of the proprietary architectures currently used. RISC-V is not new, but it gets more and more traction in Academia (no surprise).

I wanted to play with RISC-V for over a year, but finally a week ago I did one of these “hey, let’s buy that board” thing again. Sometimes these boards get on a pile to wait a few weeks or longer to get used, but that one I had to try out immediately :-).

So what would make that RISC-V interesting? Well, the instruction set and architecture is open source, so everyone could build it.

💡 Not everything is open source. The instruction set is open source, but not the actual implementation, the peripherals (UART, USB, …) or the microarchitecture implementing all the tiny steps behind the instructions. See https://news.ycombinator.com/item?id=17392461 for a discussion on this. I see an open source instruction set as a good thing, as there are no royalties to pay for using it. And open source can help prevent potential security issues, but for this an open microarchitecture would help: Spectre, Meltdown, and Foreshadow just be the most recent issue, and they are all caused by the microarchitecture implementation. But RISC-V is definitely driving more to be open source beyond the instruction set itself.

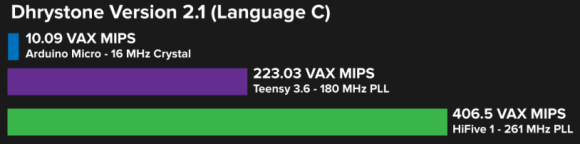

But more important: it is fast. About twice as fast as the ARM Cortex-M4F on the Teensy 3.6:

Dhrystone Benchmark Result (Source: https://hackaday.com/2017/01/05/hands-on-with-the-first-open-source-microcontroller/)

HiFive1 Board

The board costs $59 and I ordered it directly from the CrowdSupply web page. It is actually an older board and was available early 2017. It seems that newer boards are now green and not black. It features Arduino headers for adding expansion boards or easy access to the microcontroller pins.

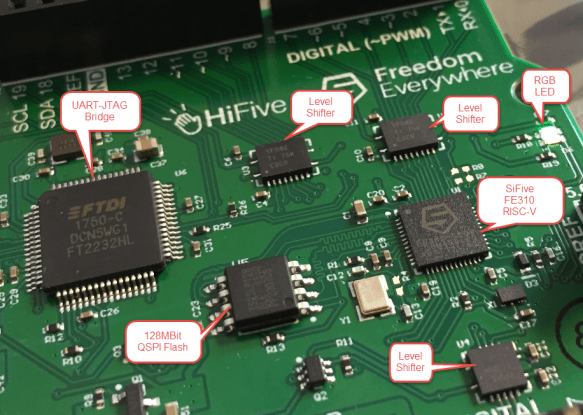

The microcontroller uses an external QSPI FLASH memory (128 MBit). The FE310 has only 16 KByte SRAM on-chip. The board can both use 3.3V and 5V logic levels as it has level shifter added.

It uses an unusual FTDI UART/JTAG interface (that bit device on the board). I rather wish they would have added a normal SWD/JTAG header to the board, which would solve lots of issues with that FTDI way. For example there is SEGGER J-Link support for RISC-V I could use *if* the board would make the JTAG signals available.

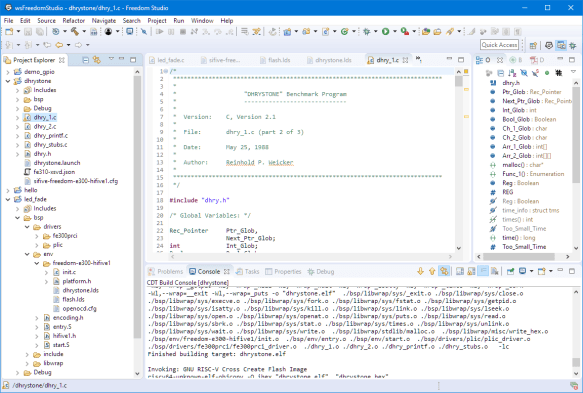

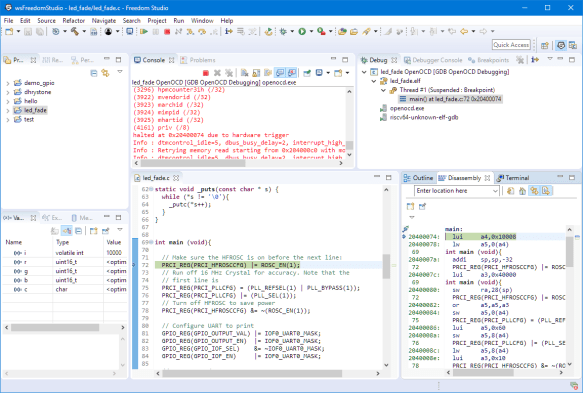

Freedom Studio

SiFive provides the Eclipse based ‘Freedom Studio’ (https://www.sifive.com/products/tools/). I have used v20180122 (beta3) on Windows 10. Download the zip file and unzip it to a folder (I used C:\Eclipse\FreedomStudio). It includes the GNU MCU Eclipse plugins for SiFive.

Examples

SiFive has a few examples installed in FreedomStudio\SiFive\Examples which I can import into the Eclipse workspace (File > Import > Existing Projects > Archive).

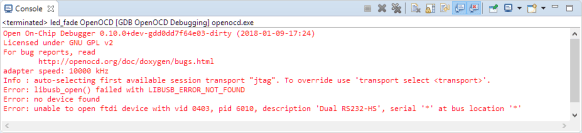

Debug Drivers

The HiFive1 board uses a FTDI device as interface for JTAG to the microcontroller. But by default Windows (and other OS) assume the FTDI is a normal USB-to-Serial device, and not a JTAG debug device. There is a detailed description of the issue on GNU MCU Eclipse. When I tried to use the board the first time, I only had errors with OpenOCD:

Open On-Chip Debugger 0.10.0+dev-gdd0dd7f64e03-dirty (2018-01-09-17:24) Licensed under GNU GPL v2 For bug reports, read http://openocd.org/doc/doxygen/bugs.html adapter speed: 10000 kHz Info : auto-selecting first available session transport "jtag". To override use 'transport select <transport>'. Error: libusb_open() failed with LIBUSB_ERROR_NOT_FOUND Error: no device found Error: unable to open ftdi device with vid 0403, pid 6010, description 'Dual RS232-HS', serial '*' at bus location '*'

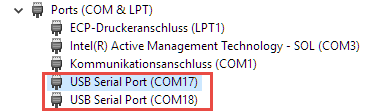

Checking the devices in the Windows Device Manager showed this:

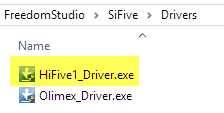

Running the HiFive1_Driver.exe in FreedomStudio\SiFive\Drivers and updating the drivers did not work, and I tried that several times. What eventually worked was:

- Reboot Windows

- Connect the board

- Run HiFive1_Drivers.exe

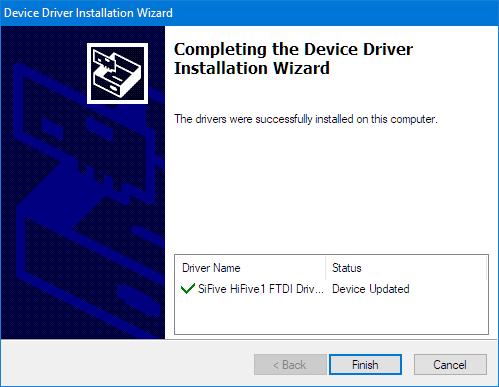

Running the installer again:

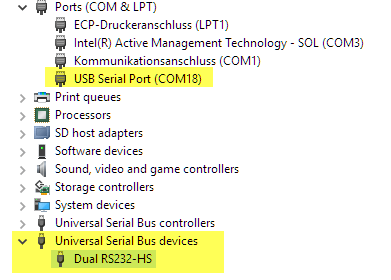

And now the drivers were properly installed:

Not sure what the problem was, maybe because I had to have the board connected while installing the drivers?

Eclipse!

Finally I was able to debug with Eclipse the HiFive1 board :-):

Summary

The HiFive1 board is rather expensive compared to other boards, and that FTDI bridge is ugly (and closed source): a normal SWD/JTAG header would be much more useful and would cost less. OpenOCD works, but it would be good to have more and better options. The really good thing is that the Freedom Studio is Eclipse based, or you can build a DIY IDE with all the components available, so no need for proprietary tools at all.

💡 SiFive has as well a ‘Linux capable‘ device. So I think we might hear from RISC-V architectures more and more. And in June 2018 SiFive announced two now cores for the lower end of computing

In a nutshell, I get better performance than the usual ARM cores and it is open source. And I think with RISC-V available more and more, it has the potential to change the industry. RISC-V is not the mass market yet, but I think this is going to change.

A next step for me would be to explore more the SDK and have FreeRTOS with my library working on that board :-).

Happy RISCing:-)

Links

- HiFive1 board: https://www.crowdsupply.com/sifive/hifive1/

- RISC-V web page: https://riscv.org/

- SiFive HiFive1 board: https://www.sifive.com/products/hifive1/

- SiFive Freedom Studio: https://www.sifive.com/products/tools/

- GNU MCU Eclipse: https://gnu-mcu-eclipse.github.io/

- GNU MCU Eclipse with FTDI JTAG drivers: https://gnu-mcu-eclipse.github.io/arch/riscv/ftdi-jtag-drivers/

- OpenOCD discussion: https://sourceforge.net/p/openocd/mailman/openocd-devel/thread/2EB30177-493F-47EA-AE8E-D6810045155F%40livius.net/#msg35882522

- libusbk on SourceForge: https://sourceforge.net/projects/libusbk/

Cool article, thanks for sharing! I was thinking of trying out one of these boards myself.

However, I think you are a bit confused about ISA, architecture, and microarchitecture. Microarchitecture,

is the CPU implementation in hardware that implements the ISA. Architecture is the combination of both the ISA and microarchitecture. RISC V is just an open source ISA. SiFive chips have a closed source microarchitecture that inplements the open source RISC V ISA. Additionally, the Spectre, Metldown, etc… vulnerabilities occur at the microarchitecture level. That is why really old x86 chips without speculative execution don’t have these vulnerabilities. Thus, the RISC V ISA being open source has nothing to do with the potential for speculative execution vulnerabilities on SiFive chips.

LikeLike

Yes, you are correct, and thanks for the feedback. Indeed, that could cause a confusion, so I have added a paragraph with more information about this topic.

Thanks again!

LikeLike

Pingback: Debugging the RV32M1-VEGA RISC-V with Eclipse and MCUXpresso IDE | MCU on Eclipse

I am a first time user on the board and it has been a painful process. I finally was able to get OpenOCD to work but now I am getting No J-Link device found. Advise/help.

LikeLiked by 1 person

Hi David,

did you remap the USB driver for the J-Link to use it with OpenOCD? In that case you have to revert the driver remapping. See https://mcuoneclipse.com/2019/09/22/eclipse-jtag-debugging-the-esp32-with-a-segger-j-link/ on that topic using an ESP32 in that article, but the same applies to RISC-V and OpenOCD.

LikeLike